## **Learning Outcomes**

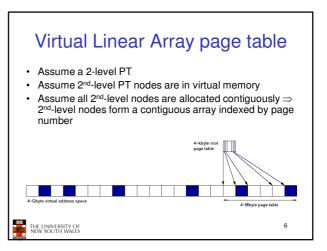

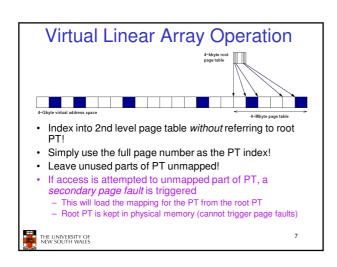

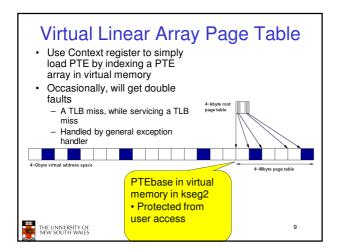

- An understanding of virtual linear array page tables, and their use on the MIPS R3000.

- Exposure to alternative page table structures beyond two-level and inverted page tables.

2

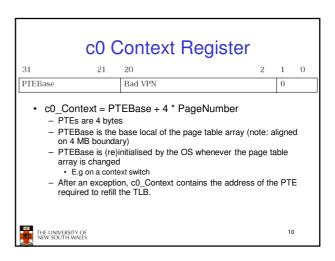

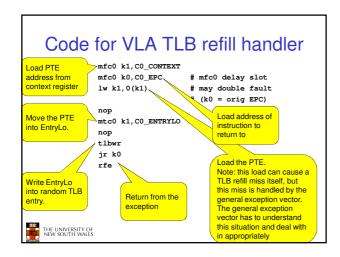

### R3000 TLB Refill Can be optimised for TLB refill An example routine mfc0 k1, C0\_CONTEXT - Does not need to check the mfc0 k0,C0\_EP; # mfc0 delay exception type # slot Does not need to save any registers It uses a specialised assembly routine that only uses k0 and k1. lw k1,0(k1) # may double # fault (k = orig EPC) nop mtc0 k1,C0\_E Does not check if PTE exists Assumes virtual linear array – see extended OS notes tlbwr jr k0 With careful data structure How does this choice, exception handler can be made very fast work? THE UNIVERSITY OF NEW SOUTH WALES

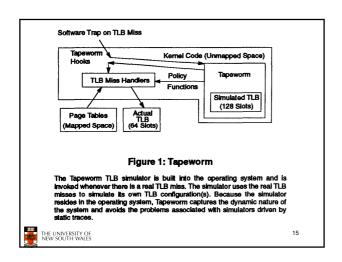

## Design Tradeoffs for Software-Managed TLBs David Nagle, Richard Uhlig, Tim Stanley, Stuart Sechrest Trevor Mudge & Richard Brown ISCA '93 Proceedings of the 20th annual international symposium on computer architecture THE UNIVERSITY OF MEN SOUTH WALES

## Trends at the time Operating systems - moving functionality into user processes - making greater use of virtual memory for mapping data structures held within the kernel. RAM is increasing - TLB capacity is relatively static

## Statement:

- Trends place greater stress upon the TLB by increasing miss rates and hence, decreasing overall system performance.

- True/False? How to evaluate?

14

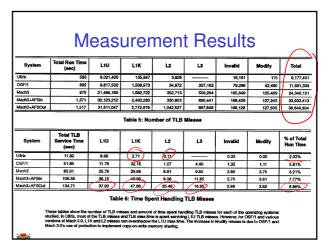

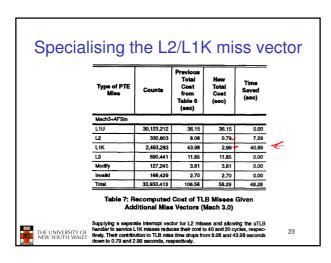

| TLB Miss Typ                                                                                          | e Ultrix                                                                                                             | OSF/1                                                                     | Mach 3.0                                                    |  |

|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------|--|

| L1U                                                                                                   | 16                                                                                                                   | 20                                                                        | 20                                                          |  |

| L1K                                                                                                   | 333                                                                                                                  | 355                                                                       | 294                                                         |  |

| L2                                                                                                    | 494                                                                                                                  | 511                                                                       | 407                                                         |  |

| L3                                                                                                    |                                                                                                                      | 354                                                                       | 286                                                         |  |

| Modify                                                                                                | 375                                                                                                                  | 436                                                                       | 499                                                         |  |

| Invalid                                                                                               | 336                                                                                                                  | 277                                                                       | 267                                                         |  |

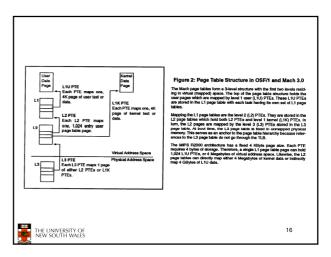

| service different typ<br>was used to collect:<br>We separate TLB in<br>that Ultrix does not<br>table. | e number of machine<br>es of TLB misses. T<br>a 128K-entry histogra<br>hiss types into the sib<br>have L3 misses bec | o determine the<br>um of timings for<br>categories des<br>ause it impleme | se costs, Monste<br>each type of miss<br>orlbed below. Note |  |

| L1U                                                                                                   |                                                                                                                      | LB miss on a level 1 user PTE.                                            |                                                             |  |

|                                                                                                       |                                                                                                                      | LB miss on a level 1 kernel PTE.                                          |                                                             |  |

| .2                                                                                                    | TLB miss on level 2 PTE. This can only occur after a miss on a level 1 user PTE.                                     |                                                                           |                                                             |  |

| L3                                                                                                    | TLB miss on a level 3 PTE. Can occur after either a                                                                  |                                                                           |                                                             |  |

An access to an page marked as invalid (page fault)

THE UNIX Invalid

## Note the TLB miss costs

What is expected to be the common case?

17

3

18

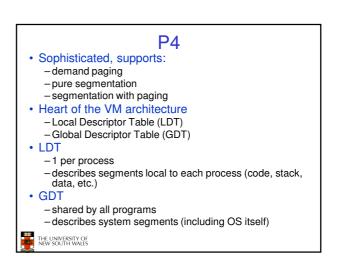

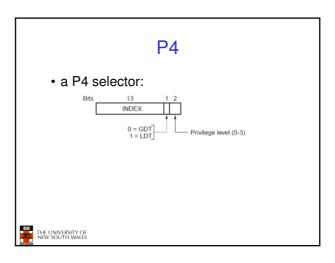

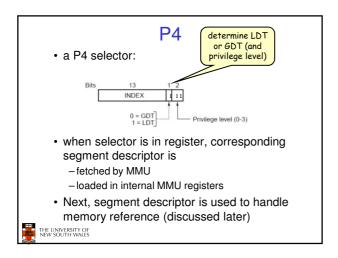

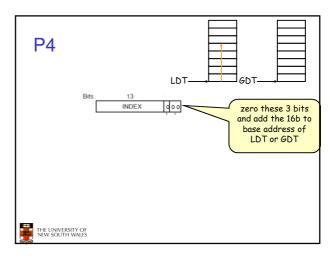

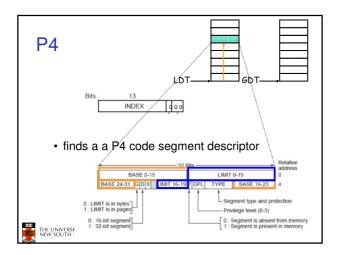

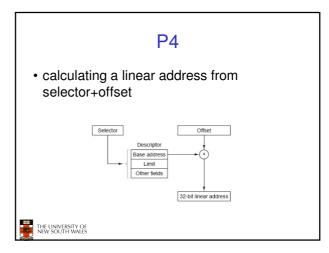

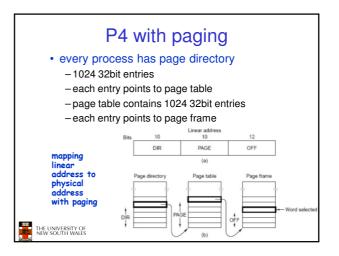

# P4 • Many OSs: -BASE=0 -LIMIT=MAX • → no segmentation at all That is it! The UNIVERSITY OF NW SOLTH WALES