## I/O Management Intro

Chapter 5

### I/O Devices

- There exists a large variety of I/O devices:

- Many of them with different properties

- They seem to require different interfaces to manipulate and manage them

- We don't want a new interface for every device

- Diverse, but similar interfaces leads to code duplication

- · Challenge:

- Uniform and efficient approach to I/O

2

### Categories of I/O Devices (by usage)

- · Human interface

- Used to communicate with the user

- Printers, Video Display, Keyboard, Mouse

- · Machine interface

- Used to communicate with electronic equipment

- Disk and tape drives, Sensors, Controllers, Actuators

- Communication

- Used to communicate with remote devices

- Ethernet, Modems, Wireless

3

### I/O Device Handling

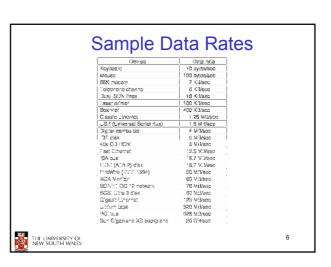

- · Data rate

- May be differences of several orders of magnitude between the data transfer rates

- Example: Assume 1000 cycles/byte I/O

- Keyboard needs 10 KHz processor to keep up

- Gigabit Ethernet needs 100 GHz processor.....

4

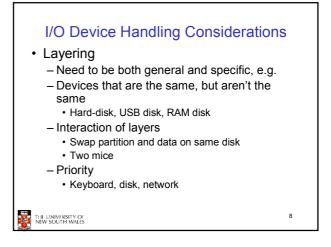

## I/O Device Handling Considerations Complexity of control Unit of transfer Data may be transferred as a stream of bytes for a terminal or in larger blocks for a disk Data representation Encoding schemes Error conditions Devices respond to errors differently 1p0: printer on fire! Expected error rate also differs "Failure Trends in a Large Disk Drive Population"; Eduardo Pinheiro, Wolf-Dietrich Weber and Luiz Andr' Barroso — USENIX FAST '07

THE UNIVERSITY OF NEW SOUTH WALES

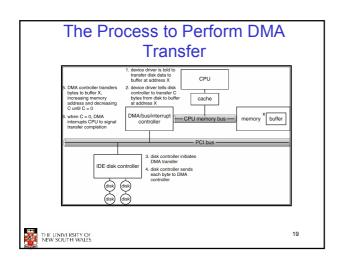

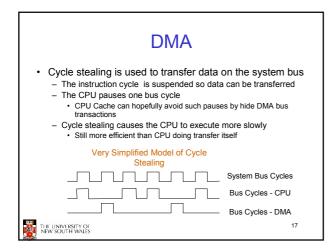

# Commonly burst-mode is used CPU uses several consecutive cycles to load entire cache line DMA writes (or reads) a similar sized burst Reason: More efficient (less cycles overall) to transfer a sequence of words than a word at a time. No bus arbitration, read/write setup, or addressing cycles required after first transfer. Number of required busy cycles can be cut by Path between DMA module and I/O module that does not include the system bus